互连方面各不相同(图3)。在MCM型的CPO中,ASIC和OE集成在封装基板上,并用铜线相互连接。随着系统带宽的要求慢慢的升高,这种结构遭遇了ASIC和OE之间的带宽密度低的问题。

有机中介层(如InFO_OS)具有ASIC和OE之间更细间距RDL(2/2 微米)的特点,可提供比MCM更高的带宽密度,因此可视为无机中介层之前的临时解决方案。[5]。

无机中介层,如CoWoS_S,具有BEOL铜互连(0.4/0.4 μm)和微凸块,通常能为通信或计算系统提供更高的带宽密度[6]。

为了减少相关成本,要避免全部使用无机中介层。我们在MCM与有机中介层的结构中,使用硅桥或LSI(CoWoS_L中的局部硅互连),来提供局部高密度电气互连网络(图4)。使用电桥可以为有机中介层提供可行的高密度互连解决方案,以扩大封装尺寸的范围,突破无机中介层的限制。

图4. 两种带有嵌入式桥梁的通用CPO结构。(A)将电桥嵌入封装基板,而 (B) 则嵌入有机中介层(如 CoWoS_L)中。

CoWoS_S和CoWoS_L都不适合需要高密度波导作为光通道来连接封装内不同OE的应用(图2. (D)和(E))。在iOIS咱们提供的CI结合了BEOL铜互连(ASIC 和OE之间)和多层介质波导系统(作为OE之间的光互连网络)。

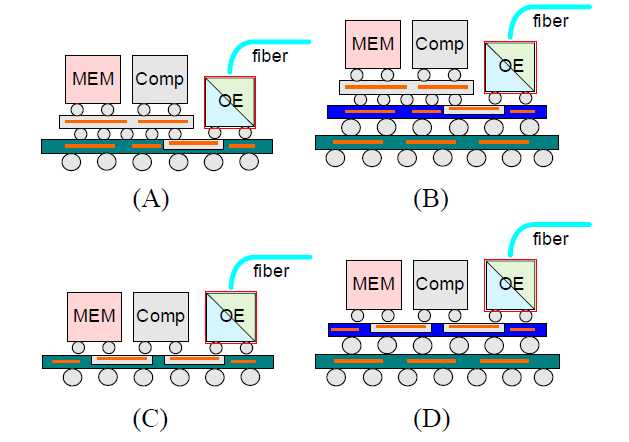

CPO结构的一种特殊形式出现在需要HBM和ASIC紧密相连的应用。在这些应用中,计算单元(如GPU)和HBM被紧密地放置在同一个无机中介层上,以获得最大的封装内电带宽。图5 (A)到(C)显示了计算-HBM模块在MCM、有机和无机中介层上面的实现。而(D)是将HBM、计算单元和OE放置在无机中介层的同一表面上的“扁平”的结构。

图5. 带有计算-HBM模块的四种CPO结构:(A)MCM、(B)有机中介层,和(C)无机中介层。(D)是(C)的扁平形式。

将计算-HBM 模块和嵌入式桥接器结合到MCM或有机中介层中,可实现图6(A)和图6(B)中的结构。(C)和(D)中有扁平版本存在。

图6. 四种CPO结构(带桥的计算-HBM模块):(A)在MCM中,(B)在有机中介层中。(C)和(D)分别是(A)和(B)的扁平形式。

PIC本身可作为无机有源光中介层。图7 (A)和(B)是一般ASIC和计算-HBM的有源光中介层结构。在这类CPO结构中,OE可以用EIC替代以进一步简化。图7(C)和(D)分别是图7(A)和(B)的简化版,而(E)是图(D)的扁平版本。

图7. 以PIC作为无机有源光中介层的五种CPO结构:(A)是主机ASIC的通用形式,而(B)则是用专门的计算-HBM模块来取代ASIC。(C)和(D)分别是(A)和(B)的简化版。(E)是(D)的扁平版本。

ASIC或计算-HBM模块也可以用单片OE作为无机有源光中介层来实现。在这种特殊情况下,具有EIC和PIC的单片OE共用同一层SOI,因此不需要单独的EIC(图8 (A)和(B))。请注意图7 (C)到(E)和图8 (A)到(B)中,光纤耦合器必须放置在有源中介层的表面上,或在有源光中介层顶部安装一个特殊的光纤采用器。这通常会增加封装工艺的复杂性。

在上述两种情况下,无论是独立的PIC或单片OE作为有源光中介层,用以承载ASIC、存储器和OE。两者都能提供硅波导层,实现芯片到芯片的封装内光互连,

不过由于使用全SOI基底面,成本比较高。此外,当ASIC直接连接到有源光互联器的顶部时,如图7(A)、(C)、(E)和图8 (A)到(B),需要一种有效的热解决方案来减轻对PIC器件的热污染。

图8. 以单片OE作为无机有源光中介层的两种CPO结构:(A)是主机ASIC的通用形式,而(B)则采用专门的计算-HBM模块来取代ASIC。

iOIS作为一个CPO平台,由COUPE2.0和CI(图 9)构成。CI具有高度集成的双光电互联(DEOI)网络,提供(1)ASIC和OE之间的电气互连,和(2) OE之间的封装内光互连网络。当CI电用于ASIC与OE之间的互连时,可提供高带宽电气互连标准的BEOL RDL。为满足ASIC与OE之间一直增长的带宽需求,与MCM解决方案相比,CI的电气接口可提供37.2倍的带宽提升,和0.19倍的能耗改善。表II是各种CPO方案电气互连的性能比较图。

当CI用于封装内芯片到芯片的光互连网络时,它可以在OE之间提供低损耗、多层波导系统。根据系统的要求,这个光路由层还可用于光功率和/或光时钟分配。由于采用了缝合技术,波导的长度不受网罩尺寸的限制。波导传播损耗可达到0.21 dB/cm,90度弯曲损耗为每圈0.009 dB。相邻波导之间的过渡损耗为0.015 dB。估计的滩前带宽密度(假设单波长和每信道100 Gbps)则约为44.9 Tbps/mm。COUPE2.0与CI之间的光接口经过特殊设计,过渡损耗仅为0.015分贝。

COUPE2.0和CI之间的超低耦合损耗为异构集成提供了坚实的基础。包括先进光学器件(如III-V激光器、半导体光放大器(SOA)、III-V族雪崩光电二极管(APD)、及其他非硅基光学器件。新增的模块化电子光学功能极大地扩展了iOIS平台的应用空间。

图9. 基于CI的CPO:(A)基本配置,(B)用于芯片到芯片的光互连,以及(C) iOIS平台的模块化电气-光学功能。请注意,所有光学元件(OE、激光器、SOA、APD、LNOI等)都与CI光耦合,耦合损耗估计约为0.015 dB。

首次提出将iOIS作为计算和通信系统的CPO平台。其两个组成部分COUPE2.0和CI可提供无与伦比的性能、功耗和设计灵活性。在COUPE2.0中,垂直宽带耦合器与嵌入式微透镜集成在一起。其损耗为0.3 dB,对准误差为10 μm。这种耦合器不仅仅具备垂直耦合器的高耦合容差和设计灵活性、还有水平耦合器的宽带解决能力。PBSR可与该耦合器集成,通过禁用光束偏转功能,该耦合器还可用作超低损耗边缘耦合器,以满足特定的系统模块设计目的。

在CI系统中,高度集成的DOOI层可提供电气互联,其电气带宽密度为37.2倍,ASIC和OE之间的能耗为0.19倍。集成的多层单模光路由层可产生0.21 dB/cm的传播损耗。90度弯曲的传播损耗为0.009 dB。相邻波导之间的过渡损耗为0.015 dB。光互联的聚合单信道滩前带宽密度可达44.9 Tbps/mm。CI接口的独特设计,使CI与COUPE2.0之间的耦合损耗仅为0.015 dB,这为未来的异构集成各种高性能非硅光学元件铺平了道路。COUPE2.0中的宽带垂直耦合器与CI中的波导系统无缝集成,从而共同为CPO光学系统模块设计提供无与伦比的性能和灵活性。

总之,作为基于3DFabric的CPO平台,iOIS能够完全满足多样化的技术需求,并产生更具成本效益的可制造的解决方案,并与代工厂的2.5D/3D路线图一致。

原文标题:【光电集成】用于高性能计算的硅基光电子应用中的集成光互连系统 (iOIS)

文章出处:【微信号:今日光电,微信公众号:今日光电】欢迎添加关注!文章转载请注明出处。

拿到一块芯片,想要使用它,首先必须要知道怎么样连线,我们用的一块称之为 89C51 的芯片,下面我们就看一

篇–动作原理–实体解剖TFT&CF功能与制程篇–ThinFilmTransistor–ColorFilterLCD背光模块篇–

展望未来,易天光通信(ETU-LINK)将继续夯实自身技术,希望为光通信市场的发展壮大贡献一份同属于光模块从业者的力量,愿有机会能为

技术重塑光模块:行业变革与突破 /

、LPO等先进封装技术在降低光模块成本及功耗上作用显著,中际旭创、新易盛等光模块厂商率先布局。

光模块技术 /

优点 /

有什么区别? 在当今的半导体技术领域,尺寸越来越小,性能慢慢的升高的芯片成为了主流。然而,随着芯片数量和面积的持续不断的增加,传统的单一芯片设计面临了慢慢的变多的挑战。为了应对这些挑战

【国产FPGA+OMAPL138开发板体验】(原创)5.FPGA的AI加速源代码

【米尔-全志T113-i开发板试用】JPG硬件编码的实现、YUV转换neon加速和对比测试

【先楫HPM5361EVK开发板试用体验】(原创)6.手把手实战红外线传感器源代码